## Homework 2

(Due date: May 25<sup>th</sup>)

Presentation and clarity are very important! Show your procedure!

## PROBLEM 1 (30 PTS)

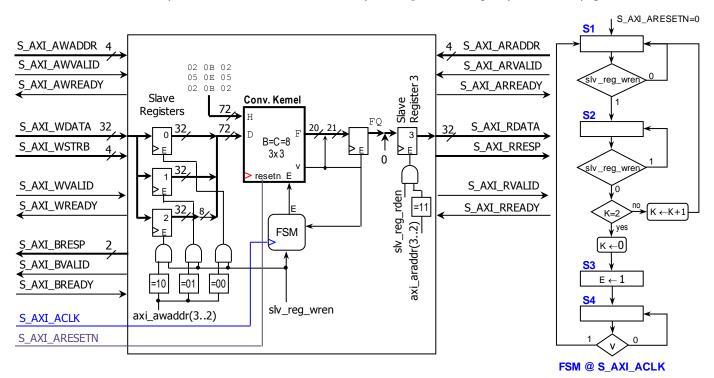

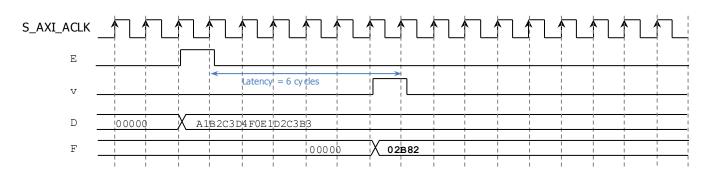

- AXI4-Lite interface for Pipelined 2D convolution kernel (N=3, B=C=8):

- $\checkmark$  The I/O timing diagram of the pipelined 2D convolutional kernel is shown below.

- Input data: 0xA1B2C3D4F0E1D2C3B3. This data is captured when E is asserted.

- Output data: 0x2B282. It appears after the processing delay (6 clock cycles) with v=1.

- ✓ Complete the timing diagram for the AXI4-Lite Interface: Given the AXI signals for the 5 Channels, complete the signals associated with the Pipelined 2D Convolution Kernel block (E, v, y, F, FQ signals) on the next page.

| myconv2_ip       | SIV          |       | READ<br>CHAI |        |           | READ ADDRESS<br>CHANNEL |         |        |               | write response<br>∽ CHANNEL           |        |       | WRITE DATA<br>CHANNEL |        |               | WRITE ADDRESS |         |        |      |

|------------------|--------------|-------|--------------|--------|-----------|-------------------------|---------|--------|---------------|---------------------------------------|--------|-------|-----------------------|--------|---------------|---------------|---------|--------|------|

| н<br>р<br>т<br>v | slv_reg_rden | RRESP | RREADY       | RVALID | RDATA     | ARREADY                 | ARVALID | ARADDR | slv_reg_wren  | BREADY                                | BVALID | BRESP | WREADY                | WVALID | WDATA         | AWREADY       | AWVALID | AWADDR | ACLK |

|                  |              |       |              |        | ·         |                         |         |        |               |                                       | ]      | ·     |                       |        | A1B2C3D4      |               | <br>}   |        |      |

|                  |              |       |              |        |           |                         |         |        |               |                                       |        |       |                       |        | 3D4           |               |         |        |      |

|                  |              |       | · ·          |        | • • - •   |                         |         |        |               |                                       |        |       |                       |        | FOELD2C3      |               |         |        |      |

|                  |              |       | · ·          |        | · • - •   |                         |         |        |               | ·                                     |        |       |                       |        |               |               |         |        |      |

|                  |              |       | · ·          |        | · • - •   |                         |         |        | <br><u></u> - | · <u> </u>                            |        |       | -+<br>-+              |        | 000/000B3     | ····          |         |        |      |

|                  |              |       |              |        | · <b></b> |                         |         |        | <u>-</u>      | · · · · · · · · · · · · · · · · · · · |        |       |                       |        |               |               |         |        |      |

|                  |              |       | · ·          |        | · • - •   |                         |         |        |               | ·                                     |        |       |                       |        |               |               |         |        |      |

|                  |              |       |              |        | • • - •   |                         |         |        |               |                                       |        |       | -+                    |        | ·             |               |         |        |      |

|                  |              | OK    |              |        |           | <u>E</u> -              | ]       |        |               |                                       |        |       |                       |        |               |               |         |        |      |

|                  |              |       |              |        | 00000000  |                         |         |        |               |                                       |        |       |                       |        | · •• •• •• •• |               |         |        |      |

|                  |              |       |              |        |           |                         | ]       |        |               |                                       |        |       |                       |        | ·             |               |         |        |      |

|                  |              |       | · ·          |        | 00102B82  |                         |         |        |               |                                       |        |       | - +                   |        |               |               |         |        |      |

|                  |              | ·     |              |        | +         |                         |         |        |               |                                       |        |       |                       |        |               |               |         |        |      |

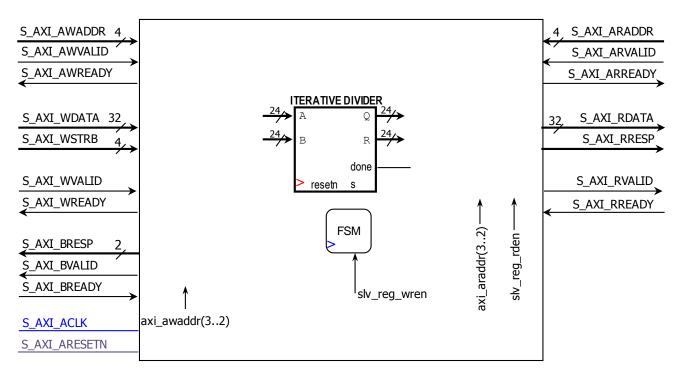

## PROBLEM 2 (35 PTS)

- AXI4-Lite interface for Iterative Divider (N=24, M=24):

- ✓ <u>Sketch the AXI4-Lite Interface</u>. This includes the Slave Registers, their control signals, as well as the extra glue logic (registers, FSM, etc.) to connect the Iterative Divider to the Slave Register signals.

- Slave Registers: Use as many as you need, indicating their number. The latched addresses depicted (axi\_awaddr[3..2], axi\_araddr[3..2]) support up to 4 registers. If for example, you need more registers (say up to 8), you would need axi\_awaddr[4..2], axi\_araddr[4..2].

- The start signal s should not be generated via software, rather it should be issued by an FSM once the input data has been received. <u>Sketch the FSM diagram (in ASM form)</u> as well.

## PROBLEM 3 (35 PTS)

Calculate the result of the following operations. The operands are signed (2C) fixed-point numbers. The result must be a signed fixed-point number. For the division, use x=5 fractional bits.

| 1.101001 + | 1001.1101 - | 0.01001 +  |

|------------|-------------|------------|

| 1.0001     | 1.010101    | 01.11011   |

| 0.10011 ×  | 1.011 ×     | 01.01110 ÷ |

| 10.101     | 1.0011      | 1.011      |

- Represent these numbers in Fixed Point Arithmetic (signed numbers). Use the FX format [16 8]. (5 pts)

- ✓ -32.1875

- ✓ 123.3125